具有场限环终端的6500V 4H-SiC结势垒肖特基二极管

随着电力系统对电力电子器件性能提高的需求不断增加,亟需提升器件的耐压、通流能力和开关速度,并降低损耗,但是硅功率器件的性能已慢慢接近其理论极限,如由其材料本身特性所决定的雪崩击穿临界电场强度以及工作温度等,然而SiC具有宽带隙、高热导率、高临界击穿电场强度、高饱和载流子速度以及其他优良的物理特性,故碳化硅是一种制作功率器件的理想的半导体材料。

同硅基pn二极管相比,SiC肖特基二极管(SBD)有很大优势,其中包含结势垒的碳化硅肖特基二极管(即SiC JBS器件)既存在pn结又存在金属半导体接触,具有开启电压小、耐压高及漏电流较小的优势,兼具了pin二极管和肖特基二极管的优点,适用于制作1.2~10kV中高压器件,在电源转换器、电动汽车、电力电子产品和远距离高压输电等电力供应设备中应用广泛。

本文报道了一种具有场限环终端的6500V 4H-SiC JBS二极管器件,介绍了设计、仿真的过程和结果,并对其进行流片和测试,器件测试结果表明;在器件电流为2A时,正向导通压降为4V,器件反向阻断电压可达8kV。

1. 器件结构设计与仿真

1.1材料参数确定

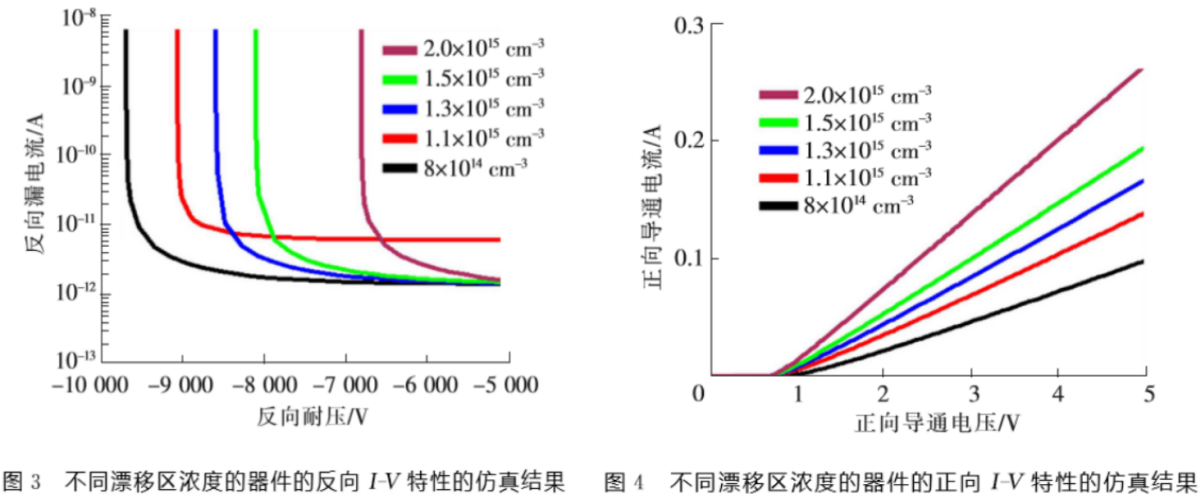

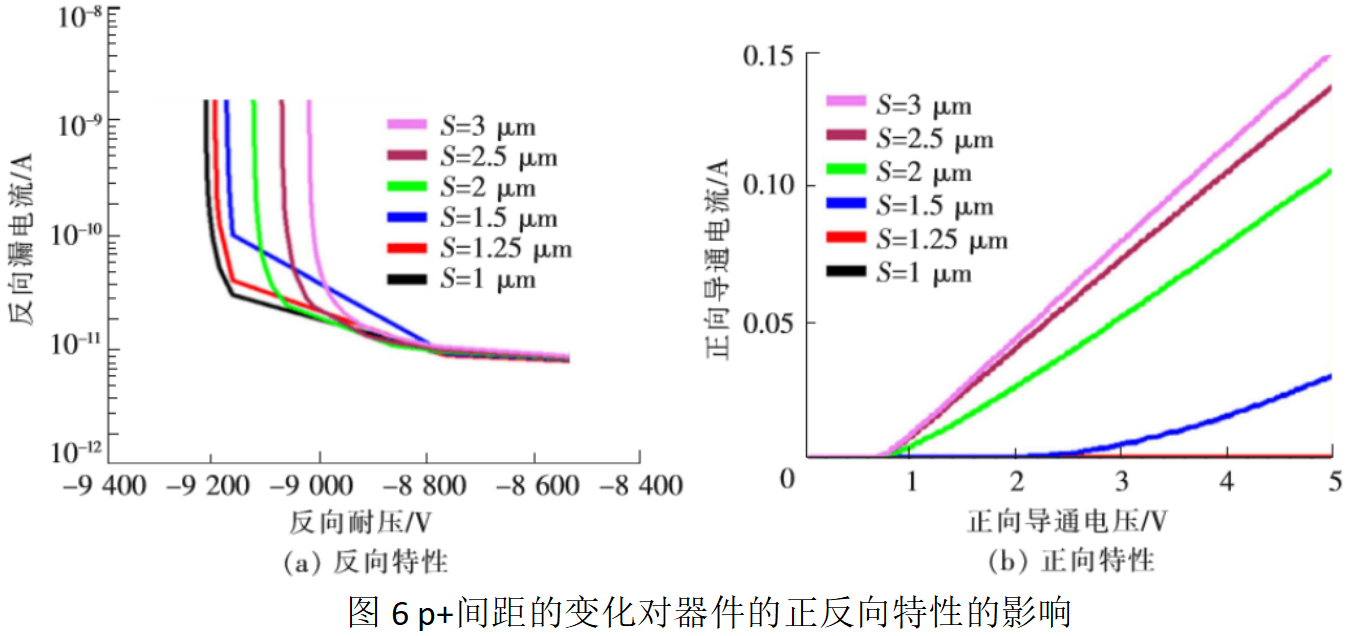

对于高压碳化硅器件,漂移层是器件承受反向耐压的部位,其参数直接决定器件的反向耐压能力的大小,漂移层掺杂浓度越低、厚度越大,器件反向耐压越高,但同时器件的通态电阻越大,为得出合适的漂移层参数,分别对其漂移层掺杂浓度和厚度的正反向特性进行仿真,采用SentaurusTCAD软件,仿真时温度设为25℃、固定JBS有源区p+型区宽度W=2µm、p+型区间距S=2.5µm。

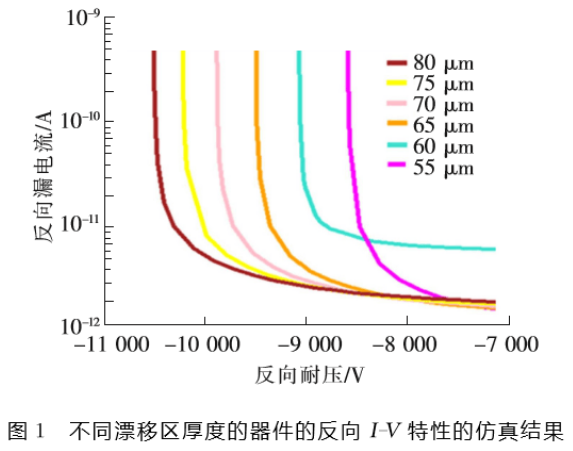

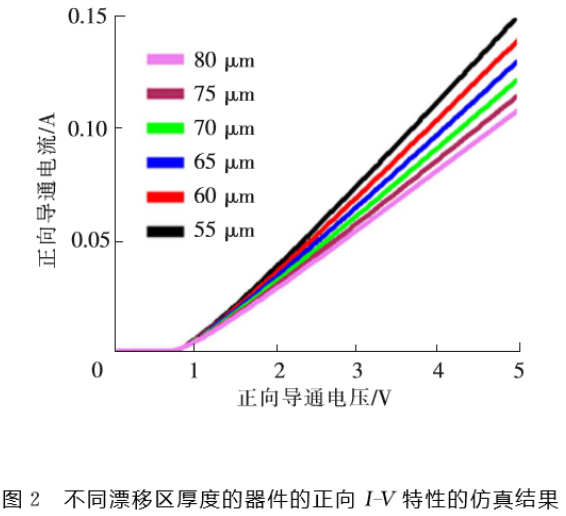

为研究漂移层厚度对器件反向特性的影响,对不同漂移层厚度进行正反向特性仿真,n-漂移区的掺杂浓度选择为1.1×1015cm-3,仿真中电压设为0~12000V,图1位器件反向特性仿真结果。当n-漂移区厚度分别为55、60、65、70、75和80µm时,耐压能力逐渐增大,从8584V增大到10510V,由于实际材料存在缺陷或器件制备过程存在工艺误差,故需要耐压值留有裕量,故要达到6.5kV的耐压,漂移层厚度选择60µm以上。

1.2 元胞结构设计与仿真

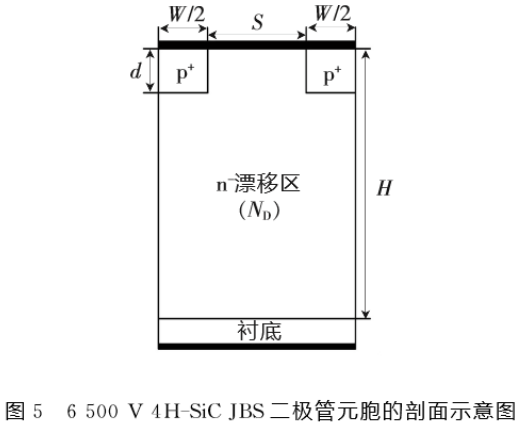

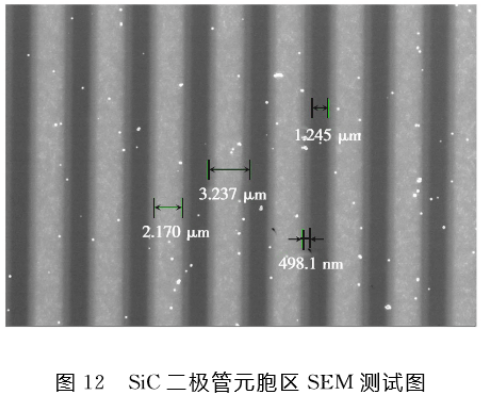

图5为4H-SiC二极管元胞的剖面示意图,二极管元胞的结构由上向下分别为肖特基接触、p-i-n区域、漂移层、衬底和欧姆接触。衬底的掺杂浓度为1×1019cm-3,漂移层厚度H为60µm,掺杂浓度Nd为1.08×1015cm-3,p+区间距为S,p+区的宽度为W,深度为d。

1.3 终端结构设计与仿真

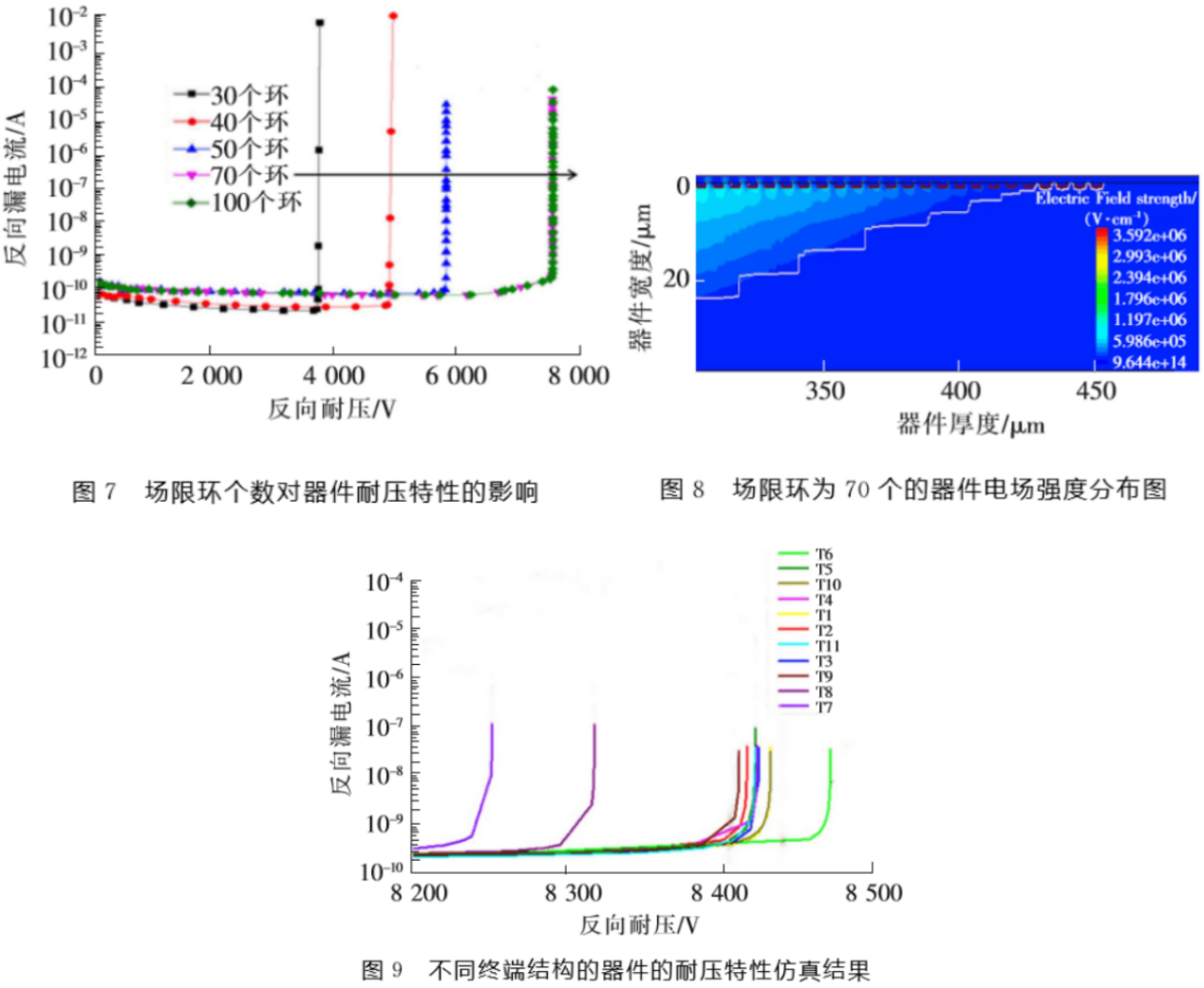

终端结构是决定器件耐压的重要因素,场限环结构是平面型高压器件主流终端保护结构之一,用来降低终端结曲率效应引起的表面电场集中,提高击穿电压。场限环结构的主要优点是结构简单,可以与主结p+注入同时形成,不必添加另外的工艺,同单区结构终端扩展(JTE)结构相比,其耐压能力对掺杂浓度相对不敏感。环的个数、场限环注入浓度、主结和环的间距、环与环之间的间距等参数都对其耐压能力有显著影响。采用SentaurusTCAD仿真工具在现有的外延材料基础上进行不同场限环结构对耐压特性的影响的仿真。图7位场限环个数对器件耐压特性影响的仿真结果,结果显示,随着环个数从30个增加到100个,耐压能力先上升,后在小于等于70个环时达到饱和,对70个环时电场强度进行仿真,仿真结果如图8所示。由图8中可看出,电场在66个环左右耗尽,其有效场限环个数为66个,为留有裕量,器件采用场限环个数为70个。通过对70个场限环宽度、间距进行优化设计,设计了11种不同结构的场限环终端,编号为T1~T11,11种不同场限环仿真结果如图9所示。仿真中电压设为0~12000V,不同的场限环终端结构下,击穿电压在8220V~8450V内变化。

根据图9的结果并综合考量终端的长度、最小线宽,评估后认为T2、T9和T10结构均可作为器件的终端结构。

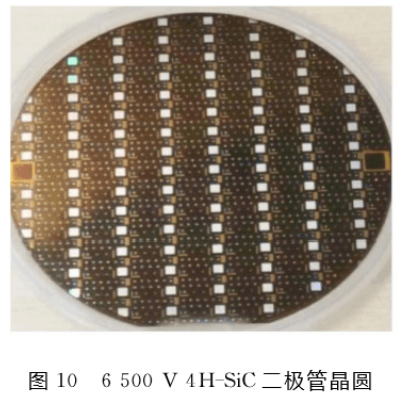

2. 器件制备

该SiC JBS采用n型外延材料,其厚度为60µm、掺杂浓度为1.08×1015cm-3,元胞p+区间距选取2.5µm。首先对样品进行表面处理,采用美国无线电公司(RCA)标准进行器件清洗,通过在500℃的条件下进行Al离子注入形成器件元胞区的p+掺杂及场限环终端,并采用溅射形成的碳膜保护进行退火,在1800℃的氩气氛围下退火10min,实现了注入后的损伤修复和激活。随后通过溅射金属Ni,并在1000℃下退火3min实现欧姆接触电极的制备。之后,通过蒸发金属Ti,并进行高温退火,实现肖特基接触电极的制备。然后采用SiO2、SiN层和聚酰亚胺制备表面钝化层。制备出6.5kV 4H-SiC JBS二极管,如图10所示。二极管芯片面积为4mm×4mm,有源区面积为2.38mm×2.38mm。

3. 流片结果测试与分析

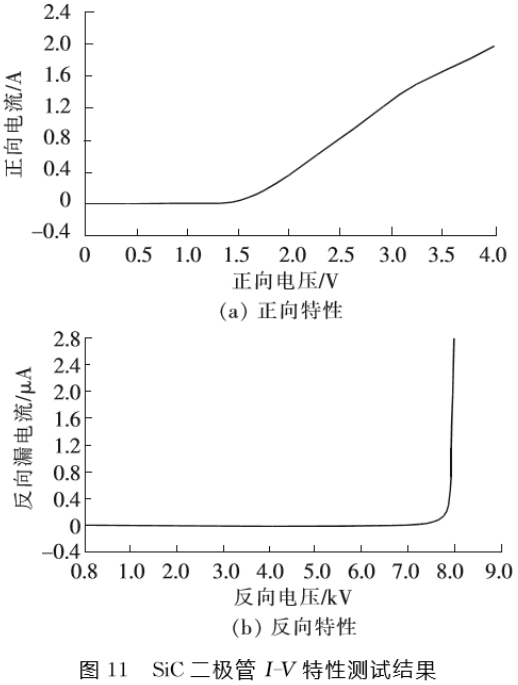

为验证器件性能,本文采用1505A功率器件分析仪及N1268A高压测试模块对器件进行测试。N1268A高压测试模块最高测试电压可达10kV。

对6500V 4H-SiC JBS二极管器件正反向特性进行测试,测试温度为25℃,测试脉冲宽度为1ms。测试结果如图11所示,器件开启电压为1.3V,在器件电流为2A时,正向导通压降为4V,因为有源区面积为2.38mm×2.38mm,故电流密度为3.53×105A/m2,器件反向阻断电压为8kV左右,终端保护效率达到95%,满足设计要求。

4. 结论

通过对器件的设计与优化制备了具有场限环终端的6500V 4H-SiC结势垒肖特基二极管,器件的开启电压为1.3V,在器件电流密度为3.53××105A/m2时,正向导通压降为4V,器件反向阻断电压最高可达8kV,终端保护效率达到96%。该器件采用场限环结构终端,有效避免了JTE终端结构因工艺原因产生的有效空穴浓度变化较大而造成的终端耐压能力下降的问题,提高了终端保护效率。

上一篇:重离子辐照1200V碳化硅二极管漏电退化的缺陷分析

下一篇:没有了