减小碳化硅二极管漏电流的混合结构

作者:海飞乐技术 时间:2017-11-03 17:55

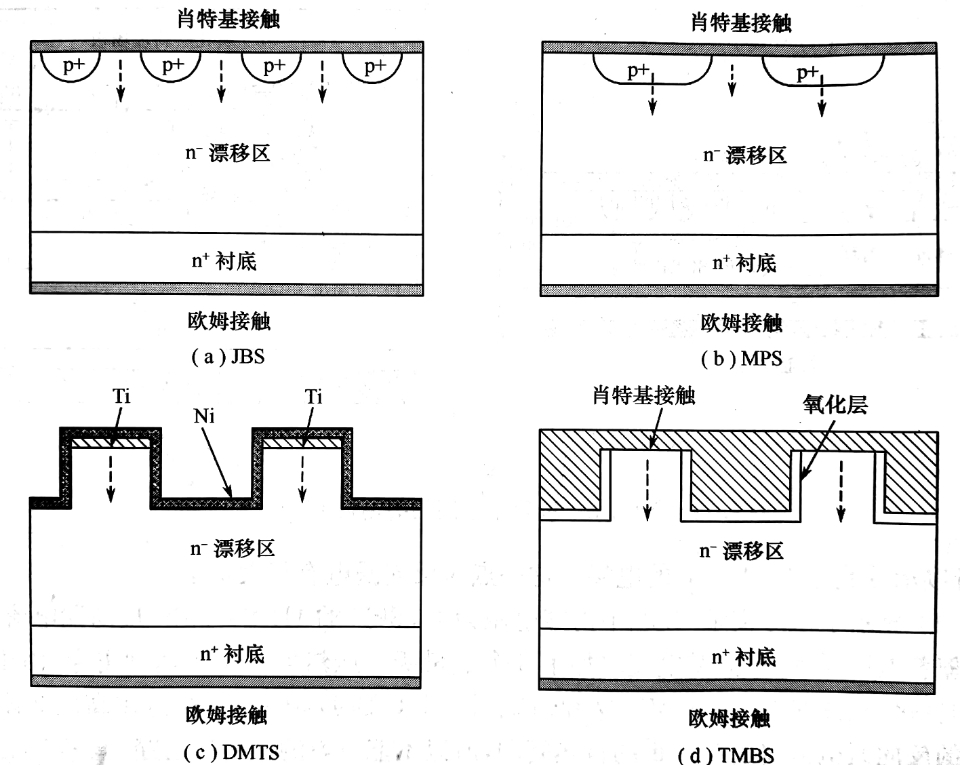

为了减小SIC SBD的反向漏电流,已经提出了多种解决方案,并产生了多种器件,其中包括结势垒肖特基二极管(JBS)、混合PIN肖特基二极管(MPS)、双金属沟槽肖特基二极管(DMTS)、双金属平面二极管(DMP)、沟槽MOS势垒肖特基二极管(TMBS)。表1中列出了近几年报道的各种减小SBD反向漏电流,增加开关电流的结构。图1中给出了不同结构的示意图。

表1 高压JBS.MPS.DMT和TMBS二极管特性(300K)

图1 基于肖特基接触的混合二极管结构所有结构均采用传统的电场屏蔽技术来减小肖特基接触电场

JBS.MPS.DMTS和TMBS结构的设计都是为了当器件处于反向阻断时,保护肖特基势垒不受高电场的影响。镜像力降低效应正是由于反向偏压增加引起的肖特基接触处电场增加导致。如图1所示,JBS和MPS采用了相同的结构,只是这两种器件的p+区设计不同。这两种结构中p+区相距很近,当器件处于反向阻断时,两个相邻的p+耗尽区互相重叠,屏蔽了高电场对肖特基接触的影响。然而在JBS结构中,p+区的深度、宽度,以及相邻p+区的间距必须仔细设计,以确保器件正常工作时p+n结不会正偏。另外,MPS的p+区设计不同,当器件的正向电流密度很大时,p+n结可以正偏,并向漂移区注入少子以减小器件的正向导通压降。要使MPS的p+n结正偏,由p+区下方产生的横向电流引起的p+n结电压差必须接近结的内建电势。由于SIC p+n结的内建电势相当高,所以需要比硅更高的电流密度才能使结开启。

DMTS和TMBS二极管中也采用了屏蔽电场原理。DMTS二极管中,邻近的沟槽中填充高势垒金属,而TMBS二极管在填充金属前先进行氧化。对于这两种情况,沟槽结构都起到了屏蔽高电场,保护肖特基势垒、减小二极管反向漏电流的作用。

横向SiC肖特基二极管,称为LMDS。另外,双金属平板(DMP)结构则具有另外一种工作原理。研究表明,SIC SBD的反向漏电流主要由器件的边缘电流引起,这是由于电场终端技术使器件的边缘电场很高。因此,制作DMP二极管时,必须在低肖特基势垒金属周围沉积第二层高SBH的肖特基金属。因为肖特基反向漏电流与SBH呈指数关系,第二层的高SBH金属减小了器件边缘高电场处的反向漏电流。器件的大部分工作区被较低的SBH肖特基接触金属覆盖,以确保低的正向压降。与前述的4种结构不同,DMP保留了平面,而且没有突出区域。

反向漏电流与温度的关系

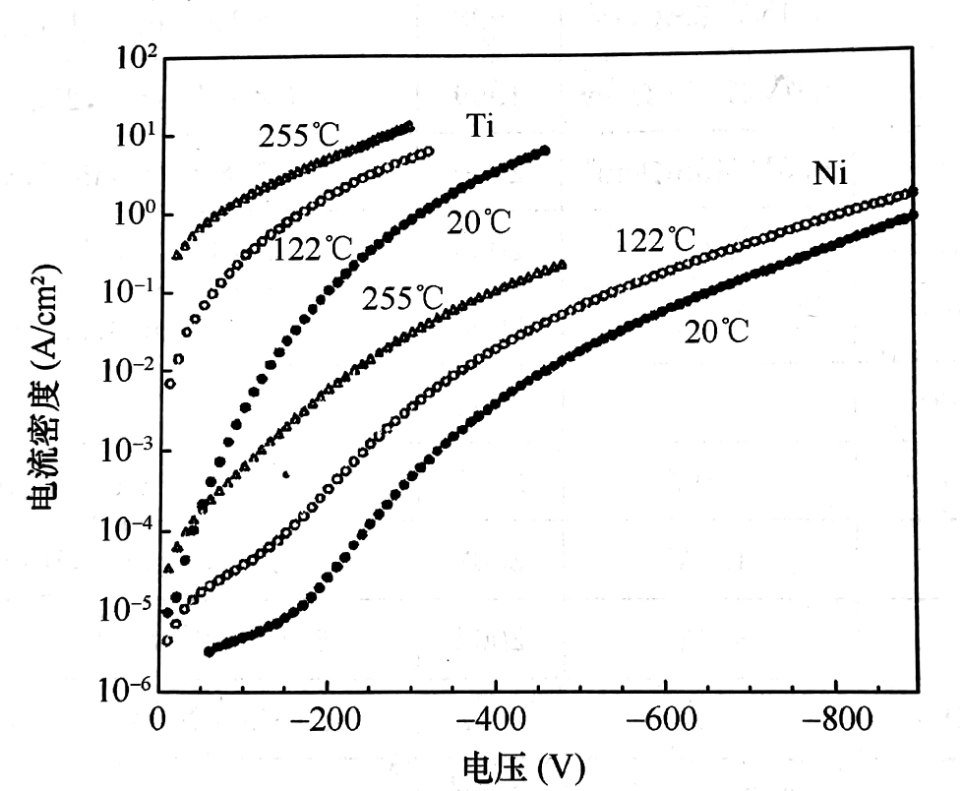

反向漏电流的热电子发射和产生-复合都与温度密切相关。图2给出了浓度为1.6×1016cm-3、厚度为10μm的Si面4H-SIC上制备的Ti和Ni肖特基势垒二极管在20℃、122℃和155℃时的反向漏电流密度。由图可以清楚看出,随着温度的增加,漏电流急剧增加,肖特基势垒高度降低。

图2 10μm、1.6×1016cm-3的Si面4H-SIC上制备的Ti和Ni肖特基势垒二极管反向漏电流密度随时间的变化

上一篇:碳化硅二极管的反向漏电流技术

下一篇:功率二极管的重要性与硅极限